Solusi Kemacetan dan Efisiensi Waktu Dengan Prototipe Traffic Light Berbasis FPGA

Dengan bertambahnya kendaraan dari tahun ke tahun tentunya berakibat pada arus lalu lintas. Suatu pengontrol arus lalu lintas pun diciptakan agar pengemudi dan pejalan kaki dapat menggunakan jalan dengan nyaman, seperti traffic light (lampu lalu lintas). Namun, apakah kinerja traffic light saat ini dapat dikategorikan baik dan efektif? Hmm.. sayangnya ada sedikit kekurangan, traffic light yang banyak kita jumpai tersebut memiliki pengaturan fase dan waktu siklus (cycle time) yang sudah tidak sesuai dengan kondisi persimpangan. Akibatnya? Macet, jumlah tundaan yang tinggi, antrian panjang dan pelanggaran adalah hal yang biasa. Solusi dari permasalahan ini adalah traffic light dengan waktu siklus dan fase yang dapat diatur dari waktu ke waktu selama 24 jam. Yup! Telah ditemukan alatnya, lampu pengontrol lalu lintas berbasis FPGA ALTERA EPF10K10 menggunakan VHDL.

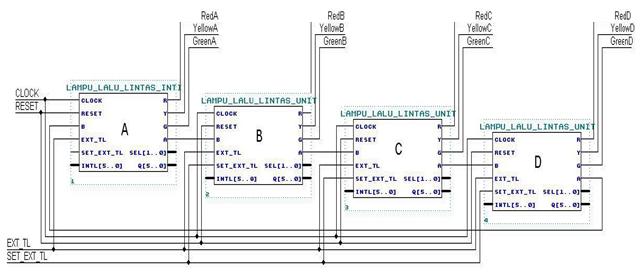

Dengan bertambahnya kendaraan dari tahun ke tahun tentunya berakibat pada arus lalu lintas. Suatu pengontrol arus lalu lintas pun diciptakan agar pengemudi dan pejalan kaki dapat menggunakan jalan dengan nyaman, seperti traffic light (lampu lalu lintas). Namun, apakah kinerja traffic light saat ini dapat dikategorikan baik dan efektif? Hmm.. sayangnya ada sedikit kekurangan, traffic light yang banyak kita jumpai tersebut memiliki pengaturan fase dan waktu siklus (cycle time) yang sudah tidak sesuai dengan kondisi persimpangan. Akibatnya? Macet, jumlah tundaan yang tinggi, antrian panjang dan pelanggaran adalah hal yang biasa. Solusi dari permasalahan ini adalah traffic light dengan waktu siklus dan fase yang dapat diatur dari waktu ke waktu selama 24 jam. Yup! Telah ditemukan alatnya, lampu pengontrol lalu lintas berbasis FPGA ALTERA EPF10K10 menggunakan VHDL.Sistem lampu pengatur lalu lintas berbasis FPGA ini dirancang dengan mendistribusikan sistem menjadi modul-modul untuk mempermudah perancangan. Selain itu, agar alat ini adaptif terhadap n-jumlah jalur pada persimpangan, maka digunakan kontrol keadaan yang terdiri dari modul lalu lintas inti dan modul lalu lintas unit. Hal ini membuat alat ini dapat digunakan pada n-jalur persimpangan, dengan cara menambah atau mengurangi modul unit pada modul kontrol keadaan ini, seperti yang terlihat pada Gambar 1. Modul A merupakan modul lalu lintas inti sedangkan modul B, C dan D merupakan modul lalu lintas unit.

Wah.. mengagumkan juga ya! Bagaimana sih cara kerjanya? Ternyata sistem pengontrol lampu pengatur lalu lintas ini bekerja dengan dua jenis kontrol yaitu kontrol manual dan kontrol otomatis.

1. Kontrol Otomatis

Lampu pengatur lalu lintas yang bekerja berdasar pewaktu (timer) pada umumnya memiliki siklus waktu yang stagnan, baik itu pada jam sibuk maupun pada malam hari. Dengan kontrol otomatis ini siklus waktu akan menjadi adaptif sesuai dengan kondisi jam yang ditunjukkan oleh modul jam digital. Keluaran dari modul jam digital akan masuk ke modul pemilih alamat memori dan menghasilkan alamat memori yang akan digunakan oleh modul memori. Modul memori berisi data-data panjang interval nyala hijau untuk tiap fase. Yang dimaksud dengan fase di sini adalah pembagian waktu jalan untuk mencegah konflik antara kendaraan dari berbagai arah yang berbeda pada suatu persimpangan.

Data-data panjang interval nyala hijau akan digunakan oleh modul kontrol keadaan untuk mengatur lama interval nyala hijau setiap fase Misalnya pada jam-jam sibuk, Sistem akan mengatur lama interval nyala hijau tiap fase lebih lama dibanding saat malam hari. Data-data panjang interval nyala hijau untuk setiap fase dalam modul memori dapat diatur oleh pengguna dengan pertimbangan berdasarkan hasil riset kepadatan lalu lintas pada waktu tertentu di suatu persimpangan. Sistem ini memiliki 12 jalur keluaran untuk lampu merah, kuning dan hijau pada 4 lajur di perempatan. Blok diagram sistem ditunjukkan pada Gambar 2.

Selain modul-modul yang sudah dijelaskan tadi terdapat modul pembagi frekuensi yang akan menghasilkan sinyal detak dengan frekuensi 1 Hz sebagi s

inyal detak bagi modul lain yang membutuhkan. Kemudian modul debouncing, untuk mengurangi efek bouncing pada tombol pengaturan. Dan modul penampil 7-segmen untuk menampilkan kondisi jam digital pada 7-segmen.

2. Kontrol Manual

Apabila kontrol otomatis dapat mengatur siklus dan interval fase lampu lalu lintas berdasarkan waktu yang didapat dari keluaran jam digital, kontrol manual bekerja dengan ditentukan oleh pengguna. Kontrol manual ini terdiri atas 2 set tombol, yaitu set tombol push button dan set tombol dip switch, seperti ditunjukkan pada Gambar 3 dan Gambar 4.

SW4 pada set tombol push button berfungsi sebagai global reset. Tombol SW3 berfungsi untuk menentukan panjang interval nyala lampu hijau pada kontrol manual. SW2 berfungsi sebagai sinyal masukan untuk hitung maju jam pada jam digital sedangkan SW1 berfungsi sebagai sinyal masukan untuk hitung maju menit pada jam digital. 8 buah dip switch yang disediakan oleh papan pengembangan dialokasikan untuk fungsi sebagai berikut: Pin 1-4 untuk sinyal masukan bagi modul pemilih lajur, pin 5-6 sebagai sinyal masukan untuk mengaktifkan sinyal hitung maju jam dan menit, Pin ke 7 untuk mengalihkan dari kontrol otomatis menjadi kontrol manual dan Pin 8 sebagai sinyal enable untuk semua sistem secara keseluruhan.

Kontrol manual ini dibuat demi kepentingan darurat saat kendaraan tertentu seperti rombongan presiden, ambulan, atau pemadam kebakaran yang memerlukan akses lalu lintas yang tak terhambat lampu merah. Fase dan lama interval nyala hijau dapat diatur sehingga jalannya tidak terhambat. Dalam hal ini, pengguna yang mengatur kontrol secara manual adalah polisi yang akan berada di pos-pos suatu persimpangan.

Hasil pengujian menunjukkan bahwa sistem lampu pengatur lalu lintas yang dirancang dengan VHDL bekerja dengan baik, untuk fungsi kontrol otomatis yang waktu siklusnya berdasarkan waktu pada jam digital maupun untuk kontrol manual yang waktu siklusnya dikendalikan oleh pengguna. Jumlah logic element yang digunakan pada perancangan sistem adalah 327 atau 56% dari kapasitas total logic element yang dimiki FPGA.

Kelebihan Alat lampu pengatur lalu lintas ini adalah sifat kontrolnya yang fleksibel, dimana pada saat kontrol otomatis, interval nyala lampu bersifat adaptif terhadap waktu, dimana datanya diambil dari analisa lalu lintas selama 24 jam yang disimpan pada modul memori dan dipilih sesuai kondisi waktu yang diperlihatkan jam digital. Alat ini juga memiliki kontrol manual dimana pengguna dapat mengatur perubahan fase dan interval nyala lampu dalam suatu persimpangan secara fleksibel saat keadaan-keadaan darurat tertentu. Penggunaan alat ini juga tidak terbatas pada perempatan, melainkan dapat disesuaikan dengan jumlah jalur yang diinginkan. Kelebihan-kelebihan inilah yang menjadikan alat ini lebih unggul dibanding lampu lalu lintas yang sering kita jumpai pada umumnya. Namun tidak ada sesuatu yang sempurna, alat ini memiliki satu kekurangan. Jika saat sumber tegangan mati, maka seluruh konfigurasi rangkaian maupun pin sandi yang tersimpan akan hilang. Tetapi hal ini dapat diatasi dengan menggunakan UPS atau baterai isi ulang sebagai sumber dayanya dan EEPROM dapat juga digunakan untuk menyimpan konfigurasi pada FPGA.

Tidak ada komentar:

Posting Komentar